| 常见信号逻辑电平标准介绍:TTL、CMOS、ECL、LVDS、CML | 您所在的位置:网站首页 › ttl 电压 › 常见信号逻辑电平标准介绍:TTL、CMOS、ECL、LVDS、CML |

常见信号逻辑电平标准介绍:TTL、CMOS、ECL、LVDS、CML

|

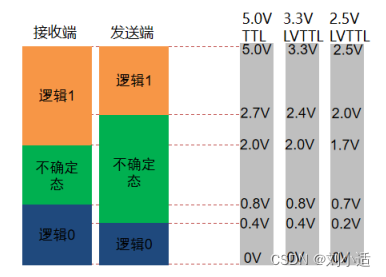

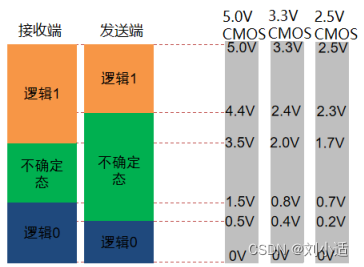

信号的逻辑电平经历了从单端信号到差分信号、从低速信号到高速信号的发展过程。单端接口具有易于设计和使用的优点,在低于300MHz的场合,单端接口被广泛使用,最基本的单端信号逻辑电平为CMOS、TTL,在此基础上随着电压摆幅的降低,出现LVCMOS、LVTTL等逻辑电平。差分信号较单端信号能够以低电压摆幅提供更大的电压增益和带宽,同时还可以去除共模和偶次谐波的干扰,从而提供更高的数据传输率。其缺点是差分信号增加了信号管脚,在PCB布线时应考虑阻抗、间距、长度等的匹配。随着高速实时性数据传输的要求越来越高,差分信号应用越来越广,常见差分信号逻辑电平有ECL、PECL、LVPECL、LVDS、CML等。 一、信号逻辑电平参数概念定义逻辑电平是指数字信号电压的高、低电平,相关参数定义如下: (1)输入高电平门限Vih:保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平; (2)输入低电平门限Vil:保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平; (3)输出高电平门限Voh:保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此Voh; (4)输出低电平门限Vol:保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此Vol; (5)阈值电平Vt:数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。它是一个介于Vil、Vih之间的电压值;对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输出,则必须要求输入高电平>Vih,输入低电平 Tips:阈值电平只是用来表征数字电路芯片的特性,实际硬件电路设计过程中具有实际意义的是Vih和Vil。 对于一般的逻辑电平,Vih、Vil、Voh、Vol以及Vt的关系为:Voh>Vih>Vt>Vil >Vol (6)Ioh:逻辑门输出为高电平时的负载电流(为拉电流); (7)Iol:逻辑门输出为低电平时的负载电流(为灌电流); (8)Iih:逻辑门输入为高电平时的电流(为灌电流); (9)Iil:逻辑门输入为低电平时的电流(为拉电流)。 二、常见信号逻辑电平参数常用的逻辑电平有:TTL、CMOS、ECL、PECL、LVDS、LVPECL、RS232、RS422、RS485、CML、SSTL、HSTL等。 1,单端信号(1)TTL和CMOS的逻辑电平按典型电压可分为四类:5V系列、3.3V系列、2.5V系列和1.8V系列,3.3V的TTL电平和CMOS电平通常称为LVTTL和LVCMOS;

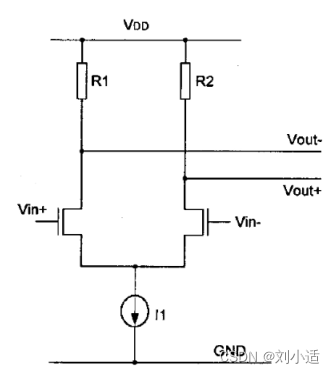

图2-1 TTL电平 图2-2 CMOS电平 (2)RS232/RS422/RS485(此处单端、差分放在一起)是串口的电平标准,RS232是单端输入输出,RS422和RS485是差分输入输出; (3)SSTL和HSTL标准:SSTL即StubSeriesTerminatedLogic标准,分为SSTL_3、SSTL_2、SSTL_18三种,对应不同的供电电压,它与LVTTL和LVCMOS的不同在于SSTL是传输线终端匹配的,因此SSTL具有输器,一般有VCCO=1.8V和VCCO=1.5V两种标准。HSTL和SSTL对参考电平要求均比较高(1%精度)。SSTL主要用于DDR存储器,HSTL主要用于QDR存储器。 2,差分信号(1)CML CML电平是所有高速数据接口中最简单的一种。其输入和输出都是匹配好的,减少了外围器件,适合于更高频段工作。CML的输入、输出缓冲电路如图所示,R1和R2是为了限制电流,通常数值相等,为50Ω。由图可以看出,该电路是差分对形式,该差分对的集电极电阻为50Ω,输出信号的高低电平切换是靠共发射极差分对的开关控制的。

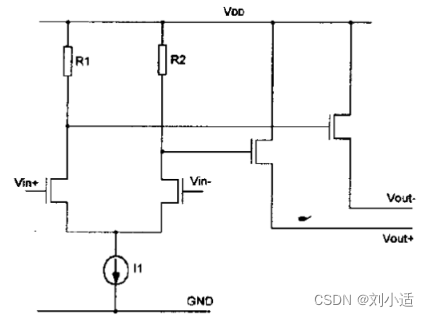

图2-3 CML示意图 (2)ECL、PECL、LVPECL ECL(EmitterCoupledLogic)即射极耦合逻辑,是带有射随输出结构的典型输入、输出接口电路,ECL电路的最大特点是其基本门电路工作在非饱和状态,正因为如此,ECL电路的最大优点是具有相当高的速度,平均延迟时间可达ns数量级甚至更少。

图2-4 ECL示意图 传统的ECL以Vcc为零电压,VEE为-5.2V电源,Vo=Vcc-0.9V=-0.9V,VOL=Vcc-1.7V=-1.7V,所以ECL电路的逻辑摆幅较小(仅约0.8V)。当电路从一种状态过渡到另一种状态时,对寄生电容的充放电时间将减少,这也是ECL电路具有高开关速度的重要原因。另外,ECL电路是由一个差分对管和一对射随器组成的,如图2所示,所以输入阻抗大,输出阻抗小,驱动能力强,信号检测能力高,差分输出,抗共模干扰能力强;但是由于单元门的开关管对是轮流导通的,对整个电路来讲没有“截止”状态,所以电路的功耗较大。 PECL(PositiveEmitterCoupledLogic)将ECL电路中的负电源改用正电源(+5V),可将Vcc接到正电源而VEE接到零点。如果采用+3.3V供电,则称为LVPECL。由图可以看出,PECL是开路输出,所以需用下拉电阻到地。不过同CML一样,LVPECL输出高低电平的摆幅因制造商不同而不同,它不仅与外部电阻有关,与逻辑门的VDD也有关。 (3) LVDS 即低电压差分信号,的驱动器由驱动差分线对的电流源组成,电流通常为3.5mA。接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过的100Ω匹配电阻,并在接收器的输入端产生大350mV约的电压。当驱动器翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑“1”和逻辑“0”状态。 常用的差分信号电平标准LVPECL、LVDS、CML的输入和输出端具有相同的门限参数。这是由产生差分信号的硬件结构决定的。 三、参考资料1, 逻辑接口_百度百科 (baidu.com) 2,详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML - 面包板社区 |

【本文地址】